PSoC y otros MCUs *mixed-signal*: adapta tus señales analógicas dentro del chip y acelera el diseño

Introducción

En electrónica de sensores, la frontera entre el mundo analógico y el digital suele resolverse con circuitería externa: op-amps, amplificadores de instrumentación, ADC dedicados, filtros activos… Sin embargo, las familias de microcontroladores mixed-signal —como Infineon PSoC, algunos STM32F3 o los nuevos PIC con Configurable Logic Blocks (CLB)— integran bloques analógicos y digitales reconfigurables en el propio encapsulado. Estos bloques abarcan desde op-amps rail-to-rail y PGAs hasta ADC ΔΣ de 20 bits y filtros digitales hardware. El resultado es una arquitectura que puede reducir la lista de materiales hasta un 35 % y comprimir semanas de validación al trasladar el front-end analógico al firmware.

¿Por qué es imprescindible adaptar las señales analógicas?

1. Impedancia y aislamiento

Sensores de puente o termistores presentan impedancias de kilo-ohmios; si se conectan sin búfer al ADC, la carga del convertidor distorsiona la medida. Un op-amp interno de alta impedancia mantiene la señal intacta.

2. Ganancia y resolución

Cuando la excursión de un sensor ocupa solo una fracción del rango del ADC, cada LSB representa demasiados microvoltios y la cuantización domina el ruido. Amplificar la señal hasta llenar todo el rango dinámico reparte el mismo error de cuantización en más niveles y aumenta la Effective Number of Bits (ENOB); cada 6,02 dB de mejora en SNR equivale a un bit adicional de resolución.

Ejemplo: un puente Wheatstone entrega ±20 mV y el ADC admite ±2 V; con una ganancia ×100 la señal pasa de ocupar el 2 % al 100 % del fondo de escala, ganando ≈ 4 bits efectivos sin cambiar de convertidor.

3. Rechazo de ruido y filtrado

Las líneas de sensor actúan como antenas de 50/60 Hz. Un amplificador diferencial seguido de filtros SC/CT y decimadores hardware —todo dentro del MCU— suprime la componente común antes de la conversión.

4. Ajuste de rango y referencia

Las referencias internas estables (por ejemplo, 1,024 V) permiten escalar la señal dentro del chip, maximizando la ventana útil del ADC y garantizando precisión térmica sin componentes externos.

Arquitectura analógica mixed-signal (vista genérica)

| Recurso interno | Función | Beneficio frente a discreto |

|---|---|---|

| Op-Amp / PGA | Ganancia ±1 × a 100 ×, modo diferencial | Sustituye INAs externos |

| Comparadores | Umbral programable, salida digital | Triggers hardware sin CPU |

| ADC SAR | 12–16 bits, >1 Msps | Lectura rápida multipunto |

| ADC ΔΣ | Hasta 20 bits, bajo ruido | Ultra-resolución para sensores lentos |

| DAC | 8–12 bits rail-to-rail | Referencias, excitación, calibración |

| Filtros HW (SC/CT + DFB) | FIR/IIR hardware | Filtrado sin ciclos de CPU |

Los MCUs mixed-signal modernos operan entre 1,7 y 5,5 V, lo que permite excitar sensores a 5 V y conversar con lógica a 3,3 V sin level-shifters.

Ejemplo detallado: balanza con puente Wheatstone (PSoC 5LP)

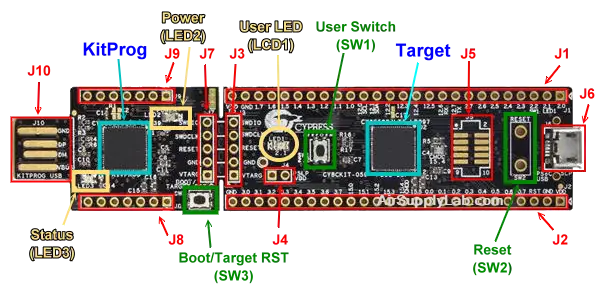

A continuación se muestra cómo construir una báscula de 10 kg con resolución práctica de ±2 g sin amplificador externo ni módulo HX711, utilizando el kit CY8CKIT-048 o CY8CKIT-059, una celda de carga estándar de 1 kΩ y el IDE gratuito PSoC Creator.

Flujo de diseño paso a paso

-

Excitación ratiométrica

- Alimenta el puente directamente con los 5 V del PSoC.

- En el panel System fija Vddio = 5 V para que las E/S analógicas trabajen a ese nivel.

-

Amplificación diferencial

- Arrastra un componente PGA al diagrama, ponlo en modo Differential y selecciona ganancia ×128 para llevar los ±20 mV del puente a unos ±2,56 V.

-

Cancelación de offset

- Inserta un AMux de dos posiciones que conmuta las entradas del PGA en cada conversión.

- El firmware resta las lecturas sucesivas (chopping), anulando el error de offset del op-amp.

-

Conversión ADC

- Añade un ADC ΔΣ de 20 bits y fija la velocidad a 240 muestras/s.

- Activa el decimador interno ×64; al promediar 64 muestras obtendrás ≈ 16 bits ENOB reales, suficientes para ±2 g en 10 kg.

-

Calibración y tara

- Guarda los coeficientes de calibración en la flash del chip.

- Utiliza DMA para volcar las lecturas del ADC a un buffer sin ocupar ciclos de CPU y aplica la tara en firmware.

Resultado

- Capacidad: 10 kg

- Resolución práctica: ±2 g

- Tiempo de prototipado: < 1 h (sin soldar ningún amplificador externo)

Todo el acondicionamiento —excitación, amplificación, filtrado y conversión— sucede dentro del microcontrolador, liberando superficie de PCB y simplificando la certificación.

Pudes leer más de este proyecto aqui

Placas PSoC recomendadas para empezar

| Placa / Kit | Microcontrolador | CPU / Flash-RAM | Analógico integrado | Headers | Rango VDD |

|---|---|---|---|---|---|

| CY8CKIT-059 | PSoC 5LP | Cortex-M3 @ 80 MHz / 256 KB-64 KB | SAR 12 bit ×2, ΔΣ 20 bit, 8 op-amps, comparadores, DFB | Breadboard + Arduino | 1,71–5,5 V |

| FreeSoC2 | PSoC 5LP (dual) | Dual Cortex-M3 @ 80 MHz / 256 KB | Igual que CY8CKIT-059 + USB FS | Arduino R3 | 1,71–5,5 V |

| CY8CKIT-048 | PSoC Analog Coprocessor | Cortex-M0+ @ 48 MHz / 32 KB | 5 op-amps, PGA, ΔΣ 20 bit, sensores integrados | Arduino-compatible | 1,8–5,5 V |

| CY8CKIT-042 | PSoC 4200 | Cortex-M0 @ 48 MHz / 32 KB-4 KB | PGA, comparadores, SAR 12 bit, CapSense | Arduino R3 + Pmod | 1,71–5,5 V |

Conclusión rápida: todas estas placas incluyen op-amps, PGA y al menos un ADC ΔΣ, eliminando la necesidad de módulos externos en prototipos de sensores de precisión.

Conclusión

Los periféricos analógicos integrados permiten medir, filtrar y acondicionar señales dentro del MCU, reduciendo la BOM y acelerando la salida al mercado. Proyectos reales muestran -35 % en coste de componentes y -40 % en time-to-market frente a arquitecturas discretas.

Además, ¿sabías que existen MCUs capaces de crear periféricos digitales personalizados mediante CLB o CLC? En el siguiente artículo veremos cómo implementar lógica discreta compleja dentro del microcontrolador para eliminar aún más hardware externo.

Contacta con InnovaPCB

Convierte tu próxima idea en un hardware fiable, optimizado y listo para fabricación. Contacta con InnovaPCB para tu próximo diseño de hardware y firmware y descubre cómo podemos impulsar tu proyecto.

Glosario de siglas

| Sigla | Significado | Explicación breve |

|---|---|---|

| ADC | Analog-to-Digital Converter | Convertidor que transforma voltajes continuos en datos binarios. |

| ADC SAR | Successive Approximation Register ADC | Convertidor que aproxima el valor binario bit a bit; rápido y de 12–16 bits típicos. |

| ADC ΔΣ | Delta-Sigma ADC | Convertidor que sobre-muestra y filtra digitalmente; ofrece hasta 20 bits de resolución. |

| AMux | Analog Multiplexer | Conmutador analógico interno que selecciona entre varias señales. |

| CLB / CLC | Configurable Logic Block / Cell | Bloques de lógica programable presentes en algunos MCUs para crear periféricos digitales a medida. |

| DFB | Digital Filter Block | Acelerador hardware que implementa filtros FIR/IIR sin cargar el procesador. |

| DMA | Direct Memory Access | Módulo que mueve datos entre periféricos y memoria sin intervención de la CPU. |

| ENOB | Effective Number of Bits | Número de bits de resolución útil después de considerar el ruido y las no idealidades. |

| PGA | Programmable Gain Amplifier | Amplificador con ganancia ajustable por software. |

| SC/CT Filters | Switched-Capacitor / Continuous-Time | Tipos de filtros analógicos internos: SC imitan resistencias con condensadores conmutados; CT son de tiempo continuo. |

| SNR | Signal-to-Noise Ratio | Relación entre la potencia de la señal y la del ruido; se mide en decibelios (dB). |